2074

Digital Logic

Full Marks: 60

Pass Marks: 24

Time: 3 hours

Attempt any two questions: (2 x 10 = 20)

Implement the following function F = ∑(0,3,5,6,7) using

- (a) Decoder

- (b) Multiplexer

- (c) PLA

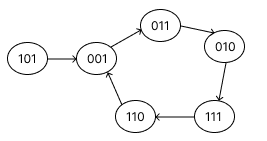

Differentiate between PAL and PLA. Design a counter as shown in the state diagram below

Draw a block diagram, truth table and logic circuit of 1*16 Demultiplexer and explain its working principle.

Attempt any eight questions: (8 x 5 = 40)

Perform the arithmetic operation (+42)+(-13) and (-42)-(-13) in binary using the signed -2’s-complement representation for negative numbers.

Express the complement of the following function in sum of minterms.

F(A,B,C,D) = ∑(0,2,6,11,13,14)

Reduce the following function using k-map

F = wxy + yz + xy’z + x’y

Design a combinational circuit with three inputs and six outputs. The output binary number should be the square of the input binary number.

Design a 5 x 32 decoder with four 3 x 8 decoder with enable and one 2 x 4 decoder. Use block diagrams only.

Design and explain the Decimal adder with truth table and suitable diagram.

Explain shift register with parallel load. Highlight on its practical implications.

Explain master slave J-K flipflop.

Write short notes on (any two):

- (a) State diagram

- (b) De-Morgan’s theorem

- (c) TTL